Abstract

A “wall plug” single-chip source of photon pairs, a fundamental building block of most quantum photonic systems, will be demonstrated having a high efficiency, rate and reconfigurability to produce factorizable quantum states and allow heralding of pure single photons. No such integrated device exists despite the fact that a rack-mounted fiber-nonlinearity-based source of this kind for lab use has been commercialized for almost a decade.

The proposed project aims to change the quantum technology landscape with the demonstration of a fully integrated single-chip quantum pair source system. The chip photonic circuit will contain photonic elements for pre- and post-source linear pump filtering, a resonant nonlinear pair generator, pump pulse carver to allow active matching of the pump pulse length to the source’s resonant bandwidth in order to control the produced photons’ joint spectral intensity (to yield a factorizable or other engineered biphoton states), and an ultra-low loss interface to fiber. The proposed approach addresses a number of challenges that arise in integration, on-chip filtering, and real-time control. In addition to standalone operation, the pair source will be the first implementation of an electronic-photonic quantum system-on-chip (epQSoC) and a key building block for more complex integrated quantum systems. The proposed epQSoCs will be implemented in a commercial 45nm CMOS electronic-photonic platform (with potential for integrating single-photon detectors on chip as well).

The project will create the technology framework (block libraries, tools, models and design methodologies) for low-cost, rapid innovation and design of sophisticated epQSoCs. This framework, along with associated educational materials and experiences will help create a new crop of engineers that are capable of tackling the complex, multidisciplinary nature of quantum information systems. Educational and outreach activities will provide exposure and training to a new generation of students and future leaders in this field, with special focus on underrepresented students.

Report

Final Report

Single-Chip, Wall-Plug Photon Pair Source and CMOS Quantum Systems on Chip

(NSF RAISE-EQuIP)

PIs: Miloš Popović1, Vladimir Stojanović2 and Prem Kumar3

Students: Josep Maria Fargas Cabanillas1, Imbert Wang1, Daniel Kramnik2, Anirudh Ramesh3

and Djordje Gluhović1

1Boston University, 2University of California Berkeley, 3Northwestern University

Quantum technology is rapidly developing, with 50-qubit quantum computing processors demonstrated by Intel, IBM and Google. To scale such new resources will require quantum networks. Such networks may allow the scaling of quantum processing power in a way similar to the parallelism of interconnected cores or servers in classical data centers and supercomputers. Other opportunities in sensing, imaging, cryptography/security, and other domains where the room-temperature stable quantum states of light could provide a useful resource and advantage are also arising, with the increasing readiness and relevance of silicon photonics to address industry applications.

The vision behind our project is to leverage our past experience developing advanced CMOS platforms enabling monolithically integrated electronic-photonic SoCs, comprising state of the art RF-CMOS transistor circuits with silicon photonics, to develop a new system-on-chip platform for quantum applications, and incorporating quantum capabilities. We call these electronic-photonic quantum systems-on chip (EPQSoCs). Our work aims to demonstrate a quantum photonic platform with sophisticated integrated feedback control, scalability and manufacturability enabled by advanced CMOS, high performance photonic devices, and new elements that may allow on-chip classical and quantum calibration, etc. The idea is to devise building blocks that will be reusable in design (like a quantum electronic-photonic “IP block library”) in a similar way as electronic circuit blocks are currently reused hierarchically in chip design to enable more complex systems. The first EPQSoC we are designing, as a demonstrator, is aimed to provide the function of a self-contained, “wall-plug” photon-pair source on chip. The SoC should take in only DC electrical power and CW pump-laser light (the equivalent of a “DC optical power supply”), as well as a couple of control lines, and be capable of outputting separable single photon pairs or pre-defined quantum states.

The Catalyst Foundation Supplement grant was requested to supplement the NSF EQuIP primary grant supporting this work. The additional funds were geared to 1) support additional chip packaging efforts to enhance the demonstrations, and 2) to enhance the cross-disciplinary team interaction. One of the primary goals of the NSF grant was to join a photonic devices group (Popović), an electronic-photonic circuits/systems group (Stojanović) and a quantum communication group (Kumar), and through close collaboration encourage learning each other’s languages and skillsets to enable the design of such convergent- technology systems. The joint work has led so far to the experimental demonstration of a CMOS tunable quantum-correlated photon pair source with all-on-chip, integrated pump filtering, and the first electronic- photonic photon pair source.

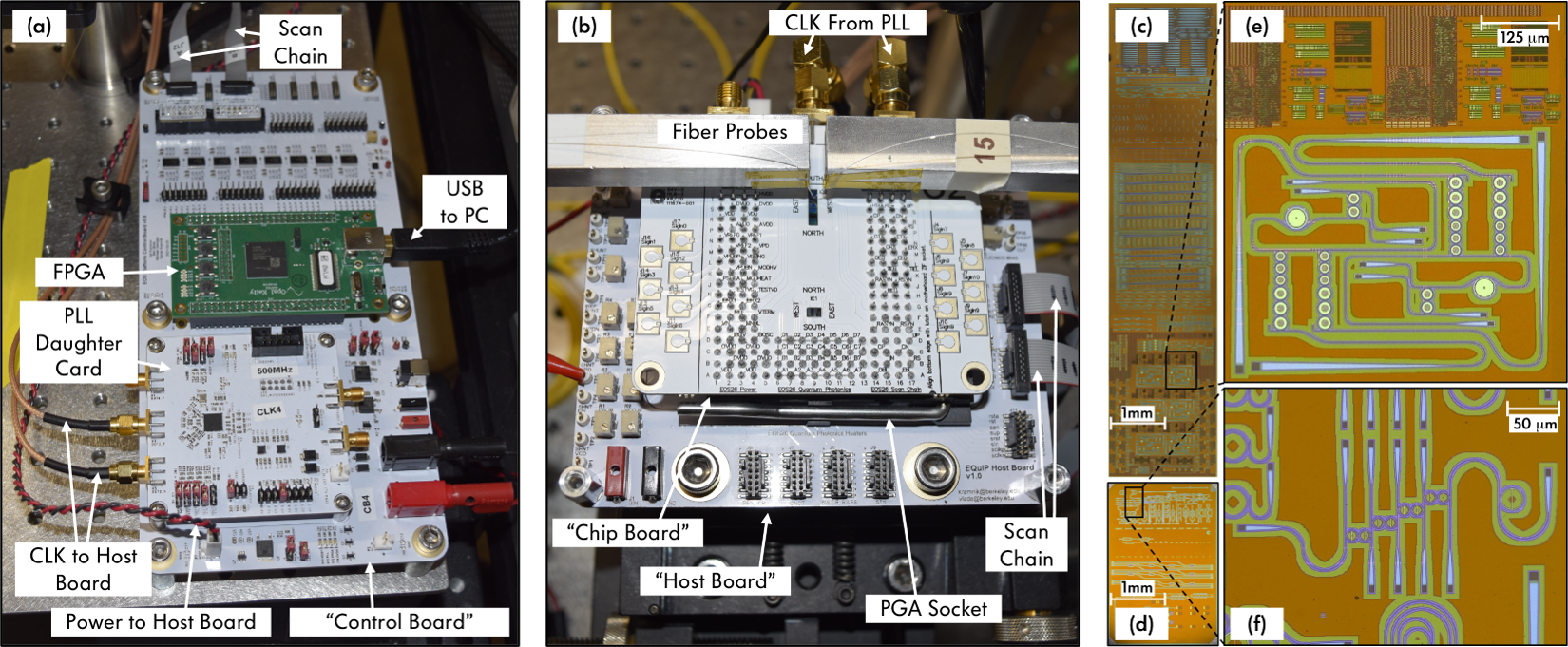

Electronic-photonic quantum systems-on-chip (EPQSoCs) developed by the Popović, Stojanović and Kumar research groups at Boston University, UC Berkeley, and Northwestern University. Shown are two SoCs implemented in the GlobalFoundries 45RFSOI CMOS platform, including an initial version of a single-chip “wall-plug” quantum-correlated photon pair source (comprising a nonlinear cavity pair generator, integrated pump filters, thermal tuning control and wavelength locking circuits, on the same chip).