# A Wirelessly Powered Log-based Closed-loop Deep Brain Stimulation SoC with Two-way Wireless Telemetry for Treatment of Neurological Disorders

Hyo-Gyuem Rhew<sup>1</sup>, Jaehun Jeong<sup>1</sup>, Jeffrey A. Fredenburg<sup>1</sup>, Sunjay Dodani<sup>2</sup>, Parag Patil<sup>3</sup>, Michael P. Flynn<sup>1</sup>

<sup>1</sup>Electrical Engineering and Computer Science, University of Michigan, Ann Arbor, MI

<sup>2</sup>Biomedical Engineering, University of Michigan, Ann Arbor, MI

<sup>3</sup>Department of Neurosurgery, University of Michigan, Ann Arbor, MI

# Abstract

A log-based closed-loop Deep Brain Stimulation system detects and processes low-frequency brain field signals to optimize stimulation parameters. The fully self-contained single-chip system incorporates LNAs, a log-ADC, digital log-filters, a log-DSP with a PI-controller, current stimulators, a two-way wireless transceiver, a clock generator, and an energy harvester. The  $2x2mm^2$  180nm CMOS prototype consumes  $468\mu$ W for recording and processing neural signals, stimulation, and for two-way wireless communication.

# Introduction

Deep brain stimulation (DBS) of the subthalamic nucleus is an effective therapy for numerous neurological disorders including Parkinson's disease, which affects more than 1.5m people in the US [1]. However current treatment systems require monthly or weekly adjustment by trained clinicians. Despite more than a decade of research, effective closed-loop optimization of stimulation parameters, which would greatly improve the treatment of the neurological disorders, remains elusive. Recently several SoCs incorporating both neural recording and stimulation have been described [2]. Spike sorting and principal component analysis (PCA) [3,4] can disentangle spikes, this approach is not effective for closed-loop DBS. Moreover spike sorting with PCA requires significant computation making RF powered or even long-term battery powered operation difficult.

We present the first wirelessly-powered closed-loop DBS SoC with RF telemetry. Our device implements stimulation control based on the analysis of Local Field Potential (LFP) energy, as proposed in recent brain research [5]. A novel log-domain signal processing chain incorporates a log-ADC, digital log-filters, and a log-DSP to improve energy efficiency and enable RF powered operation. In addition to recording and stimulation capabilities, the prototype is fully self-contained with energy recovery, voltage regulation and clock generation, to achieve a true single-chip solution. To broaden the utility of this system, the SoC also incorporates two-way wireless telemetry as well as support for optical stimulation for

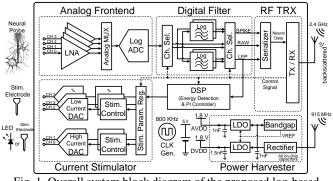

Fig. 1. Overall system block diagram of the proposed log-based closed-loop DBS system.

optogenetic research.

#### System Architecture

Fig. 1 illustrates the overall system. As neural signals are elegantly expressed in logarithmic scale, we improve energy efficiency by introducing a complete log-domain neural recording and processing chain. Four band-pass LNAs amplify neural signals and these signals are multiplexed to a 100kSample/s 8b pipeline log-ADC. A new log-ADC scheme eliminates the dead zone in earlier log-ADCs [6]. Furthermore, log-domain digital filtering is introduced to efficiently process the log-scale digital output from the ADC, saving power consumption by avoiding multiplication. Similarly, the log-DSP calculates LFP energy by simple bit-shifting instead of squaring.

Uniquely, the DSP includes a programmable PI-controller that evaluates the LFP energy to set the optimal stimulation amplitude. An advantage is that the closed-loop feedback is based on low-pass-filtered LFP signals making the closed-loop robust to high-frequency stimulation artifacts. There are six 6b general-purpose (116 $\mu$ A) stimulation channels and two 6b high-current (4.2mA) channels. The high-current channels can also drive LEDs for optogenetic applications.

For battery-less operation, an on-chip energy harvester, comprised of a rectifier and two on-chip LDOs, recovers energy to power the entire system from 915MHz RF carrier. The single-chip system also incorporates a bandgap reference, bias circuitry and a clock generator. The stimulation parameters can also be set manually via a 2.4GHz wireless downlink. The device also includes an 800kbps power-efficient backscatter RF transmitter that can communicate recorded LFP, spike or raw data wirelessly to an external receiver. Compared to [2], the prototype has complete DSP, a more efficient recording chain, two-way wireless interface, RF energy harvesting, power management and clock generation.

#### **Circuit Implementation**

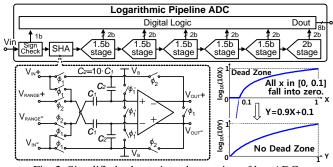

The log-ADC improves on that in [6] achieving a dynamic range of 59dB by removing the dead zone (Fig. 2), where otherwise small signals are compressed below the quantization range. The dead-zone elimination scheme is embedded in SHA

Fig. 2. Simplified schematic and operation of log-ADC.

# of the log-ADC.

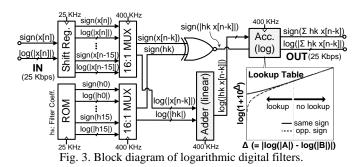

We improve energy efficiency by taking advantage of the logarithmic output of the ADC to introduce log-scale digital signal processing. The log-filters (Fig. 3) consume 48% less power than equivalent linear-filters. Low-pass and high-pass 15<sup>th</sup> order FIR filters simultaneously separate low-frequency LFPs and high-frequency spikes. The log-filters replace power hungry multipliers with adders. A look-up table method is used for logarithmic accumulation. Further power reduction is achieved by avoiding accumulation when the difference of the two inputs is larger than a threshold where the output is simply and accurately approximated as the larger input. The log approach also simplifies the PI-controller, which optimizes stimulation amplitude based on LFP energy. Moreover, instead of squaring, simple 1b left-shifting determines the energy of the log-domain LFP signals in the log-DSP.

The LNAs consist of a cascade of two band-pass filters. The current stimulators include parameter registers, biphasic stimulation controllers, and 6b current DACs. Backscattering modulation is exploited in the transmitter to minimize power consumption, achieving an energy consumption of 6.25pJ/b. The receiver demodulates a PWM input to set the parameters of the PI-controller and the stimulators.

The system is entirely powered by the RF energy harvester except for the high-current DACs, which require a 5V battery. A full-wave self-threshold-compensated rectifier based on [7] has the body of each FET tied to the drain for lower on-resistance and less reverse-bias leakage. A source-coupled relaxation oscillator generates the 800kHz system clock.

#### **Measurement Results**

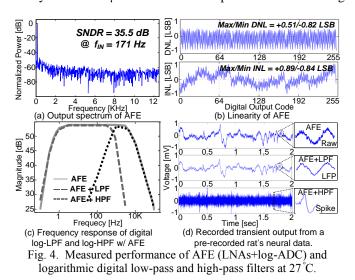

The prototype is fabricated in 180nm CMOS and occupies  $2x2 \text{ mm}^2$  (Fig. 7). The measured total power consumption of the system is 468µW. The measured performance of analog

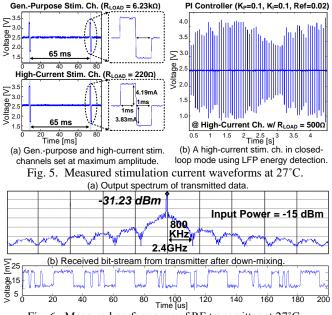

Fig. 6. Measured performance of RF transmitter at 27°C.

frontend (AFE: log-ADC + LNAs) and digital log-filters is shown in Fig. 4. The SNDR and maximum DNL/INL of the AFE are 35.5dB and 0.82 LSB/0.89 LSB respectively. The LNAs achieve a measured gain of 54dB over a passband from 0.64Hz to 6kHz. Both the digital low-pass and high-pass filters have the 3dB cutoff frequency of 700Hz. Measured raw, LFP and spike recordings of a pre-recorded rat-brain neural signal recorded by the prototype are also shown in Fig. 4. Fig. 5 shows measurements of stimulation current pulse trains. As demonstrated in Fig 5 (b), the closed loop system adapts the stimulation current in real-time responding to the energy of input LFP signals. Fig. 6 shows the measured output spectrum and transmitted bit stream of the backscatter transmitter.

| 1   | LNA    |                                       |                           |                           |

|-----|--------|---------------------------------------|---------------------------|---------------------------|

|     | CH 0   | CH 5                                  | AFE Power                 | 245 µW                    |

|     | CH=1   | Log ADC                               | Digital (Filter + DSP +   | 129W                      |

|     | CH 2   | CH 1 CH 2                             | Stim. Controller) Power   | 138 µW                    |

| . 5 | CH-3   | Bias CLK                              | TX/RX Power               | 5/4.6 µW                  |

|     | LDO    | Digital හි :                          | Total Power               | 468 µW                    |

| 2   |        | (Filter + DSP +<br>Stim. Control) TRX | Estimated Rectifier Power | 52% @ I <sub>LOAD</sub> = |

| 2   | Bandga |                                       | Conversion Efficiency     | 350 µA                    |

| h.  |        |                                       |                           |                           |

Fig. 7. Die photo and power breakdown for the prototype system.

#### Conclusions

We present the first fully self-contained wirelessly-powered closed-loop DBS SoC based on the analysis of LFP energy with RF telemetry. Log-domain signal processing improves energy efficiency allowing wirelessly powered operation. This work was funded in part by the Catalyst Foundation.

### References

- [1] M.L. Kringelbach, et al., *Nature Reviews Neuroscience*, Aug. 2007.

- [2] J. Lee, et al., *IEEE JSSC*, Sep. 2010.

- [3] T.C. Chen, et al., *ISSCC*, Feb. 2009.

- [4] M. Azin, et al., *IEEE JSSC*, Apr. 2011.

- [5] F. Yoshida, et al., J. Neurology, Neurosurgery and psychiatry, Aug. 2010.

- [6] J. Lee, et al., *IEEE JSSC*, Oct. 2009.

- [7] G. Papotto, et al., *IEEE JSSC*, Sep. 2011.